Theory of Pipelining in Computer Architecture

Need of Pipelining:

1. Circuits.

2. Re-arrangement of hardware.

P1 → O → P → R = 3s

P2 → —- —- —- O → P → R = 6s

P3 → —- —- —- —- —- —- O → P → R = 9s

Average Time ( 9/3 ) = 3s.

P1

→ O → P → R = 3s

P2

→ —- O → P → R = 4s

P3

→ —- —-

O → P → R = 5s

Average Time ( 5/3 ) = 1.66s

Difference

between Pipelined and Non-pipelined System:

|

Sr. No. |

Topic |

Pipe-Lined

System |

Non-Pipelined

System |

|

1 |

Working |

In this, multiple

instructions are overlapped during execution. |

In this, processes like decoding,fetching,execution,and writing memory

are merged into a single unit or a single step. |

|

2 |

Execution Time |

Many instructions are executed at the

same time and Execution time is comparatively less |

Only one instruction is executed at the

same time and Execution time is comparatively high. |

|

3 |

Dependency on CPU Scheduler |

The efficiency of the pipelining system

depends upon the effectiveness of the CPU scheduler. |

The efficiency is not dependent on the CPU scheduler. |

|

4 |

CPU Cycles Needed |

Execution is done in fewer CPU cycles |

Execution requires a greater number of CPU cycles comparatively |

Definition of pipelining:

1.

Pipelining is the process

of arrangement of hardware elements of CPU such that its overall performance is

increased.

2.

Simultaneous execution of

more, than one instance takes place in pipelined processor.

3. In pipelining multiple instances are overlapped in execution.

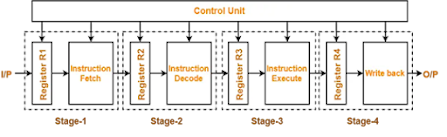

Five Stages of Pipelining:

1. Instruction Fetch (IF)

2. Instruction Decode (ID)

3. Execute (EX)

4. Memory Access (MEM)

5.

Write Back (WB)

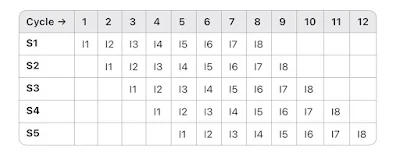

P = 8I, I1 –

I8

Where:

1. k

= Number of pipeline stages (5)

2. n

= Number of instructions (8)

1. Pipelined

Execution Time:

= k + (n - 1)

= 5 + (8 - 1)

= 5 + 7

= 12

Non- Pipelined Execution Time: 5 × 8 =

40

2. CPI

Calculation:

CPI

(Clock Cycles Per Instruction)

What is Pipelining?

Pipelining is the process of accumulating

instruction from the processor through a pipeline. It allows storing and

executing instructions in an orderly process. It is also known as pipeline

processing.

Pipelining is a

technique where multiple instructions are overlapped during execution. Pipeline

is divided into stages and these stages are connected with one another to form

a pipe like structure. Instructions enter from one end and exit from another end.

Pipelining increases

the overall instruction throughput.

In pipeline system,

each segment consists of an input register followed by a combinational circuit.

The register is used to hold data and combinational circuit performs operations

on it. The output of combinational circuit is applied to the input register of

the next segment.

Pipeline system is like the modern-day assembly line

setup in factories. For example, in a car manufacturing industry, huge assembly

lines are setup and at each point, there are robotic arms to perform a certain

task, and then the car moves on ahead to the next arm.

In general, the pipeline organization is

applicable for two areas of computer design which includes:

1. Arithmetic Pipeline:

An arithmetic

pipeline is a technologically shaped processing pipeline designed to accelerate

the implementation of arithmetic operations. It's an ideal part of the general

processor figure, particularly specializing in improving the overall

performance of mathematical computations.

Components

- Addition

Stage: In this stage, the pipeline plays the

addition operation. It's a crucial mathematical operation and is frequently

broken down into sub-parts for efficient processing.

- Multiplication

Stage: For more complicated mathematics

operations, which encompass multiplication, an intense level is covered in

the pipeline. Multiplication consists of a sequence of partial products,

and an arithmetic pipeline can simplify this device.

- Division

Stage: Division is any other arithmetic operation

that can take advantage of pipelining. Dividing various involves more than

one step, and breaking down the approach into pipeline ranges can decorate

the general tempo of execution.

Advantages:

- Parallelism

in Arithmetic Operations: Arithmetic pipelines

take advantage of parallelism by breaking down complex operations into

small parts. This allows the concurrent execution of a couple of

arithmetic operations, considerably enhancing throughput.

- Optimized

Resource Utilization: The pipeline structure allows

for the best usage of processing resources. While one arithmetic operation

is within the multiplication stage, every other can be within the addition

stage, maximizing the performance of the processor.

- Enhanced

Computational Speed: By dividing arithmetic

operations into smaller, feasible phases, the overall pace of computation

is expanded. This is mainly critical in programs in which mathematical

calculations are a large element, which includes medical computing or

photograph processing.

2. Instruction Pipeline:

An Instruction

Pipeline is a key component of a processor's structure designed to facilitate

the concurrent execution of a couple of commands. It breaks down the execution

of instructions into different phases, allowing one-of-a-type spans to function

simultaneously on unique instructions.

Components:

- Instruction

Fetch (IF): The first stage entails

fetching the instruction from memory. The software program counter is used

to decide the address of the following approach.

- Instruction

Decode (ID): In this phase, the fetched

instruction is decoded to determine the operation to be completed and to

understand the operands involved.

- Execution

(EX): The actual computation or operation through

the instruction takes place in this stage. It might also additionally

contain mathematics or logical operations.

- Memory

Access (MEM): If instruction requires access

to memory, this stage is wherein data is analyzed from or written to

memory.

- Write

Back (WB): The final phase includes

registering the results once more to report or memory and finishing the

execution of these.

Advantages:

- Improved

Throughput: The instruction pipeline allows

for a continuous drift of commands through the processor, enhancing the

usual throughput. While one instruction is within the execution phase,

every other may be within the decoding phase, resulting in better resource

utilization.

- Faster

Program Execution: By overlapping the execution of

instructions, the time taken to execute a series of commands is reduced.

This outcome in faster software execution is a vital element in enhancing

the general performance of a PC system.

- Effective

Resource Management: Instructional pipelining allows

powerful manipulation of sources by permitting tremendous levels of the

pipeline to operate concurrently. This contributes to a good and

streamlined execution of commands.

.jpg)

0 Comments